# Performance Evaluation of the Ultra High-Speed Synchronous Arbitration for Transient Pixels' Events

A.N. Belbachir, Member IEEE, M. Hofstätter, M. Litzenberger and P. Schön

Austrian Research Centers GmbH - ARC smart systems Division Donau-City-Strasse 1 -1220, Vienna, Austria

{ahmed.belbachir, michael.hofstaetter, martin.litzenberger, peter.schoen}@arcs.ac.at

Abstract— In this article, an ultra high-speed synchronous arbitration process for transient pixels' data is presented and evaluated. Enabling a high-precision timestamping, this system demonstrates its uniqueness for handling high peak rates and preserving the main advantage of the neuromorphic electronic systems, that is high and accurate temporal resolution of the pixels' events. By attaching a timestamp to the event at its occurrence instant, the synchronous arbitration concept provides accuracy better than 1  $\mu$ s. Both synchronous and (state-of-the-art) asynchronous arbiters are implemented in a neuromorphic dual-line vision sensor chip in a standard 0.35  $\mu$ m standard CMOS process. The performance analysis of the synchronous arbitration is provided and discussed for highspeed applications.

#### I. INTRODUCTION

Biologically-inspired vision electronics has recently drawn emerging interest owing to their low-cost and low power advantages as well as to the enduring motivation in rebuilding part of the human vision mechanism. The main concern of these systems is the representation of information by relative values of analogue signals, rather than by absolute values of digital signals as argued by Carver Mead [12].

Vision models have been built in sensors like the one of Mahowald and Mead [10] [11], originally named the "silicon retina" sensor. In succession, a large variety of diverse silicon-retina sensor designs have been carried out and reported, including gradient based sensors sensitive to static edges [6], temporal contrast vision sensors that are sensitive to relative light intensity changes [8][13], orientation selective spiking neurons devices [9] from Delbrück and group in ETH Zürich and optical flow sensors [4] from Bernabe Linares-Barranco.

The temporal contrast vision sensors focused on in this paper feature massively parallel pre-processing of the visual information by on-chip analogue circuits and are commonly characterized by high temporal resolution, wide dynamic range and low power consumption. Each pixel operates autonomously and responds with low latency to relative illumination changes by generating asynchronous events [13]. It generates two types of events, which represent a fractional increase or decrease in light intensity that exceeds a tunable threshold. Combined with the pixel address, these events are referred to as 'Address-Events' (AE) [5]. Unlike frame-based CMOS sensors, neuromorphic imagers require an arbiter to organize the access of multiple asynchronous data sources (pixels) to a common communication bus. As the pixels are autonomous, several pixels can generate AE instantaneously and therefore, the AE interface (arbiter) is needed to arbitrate the transfer of temporally concurrent events via the common communication bus.

K.A. Boahen [2][3] has developed AE communication circuits for the events transmission. This asynchronous AE interface handles temporally coincident pixels' events for up to  $10^6$  AE/ second. However, the digital timing information is not on-chip allocated to the AE and has to be provided by an external unit (e.g. from the processing unit). Furthermore, the arbitration process is not deterministic.

For this reason, we have developed a synchronous AE interface [7] for deterministically arbitrating between multiple asynchronous sensor elements and adding a timestamp to the AE at the generation time, for preserving ultra-high precision temporal information. Both arbiters [2] and [7] have been implemented in a temporal contrast vision dual-line sensor chip [13] where only one of them can be activated at a time for data acquisition.

This paper presents a performance evaluation of the synchronous arbitration of temporally concurring AE using the dual-line sensor chip for high-speed vision applications. The paper is structured as follows. In Section II, the notion of arbitration is introduced and described. The characteristics of the synchronous AE communication interface are summarized in section III. Section IV presents a performance analysis and experimental results of the dual-line sensor and the arbiters for high-speed vision. A summary is given in Section V.

#### II. WHY AN ARBITER?

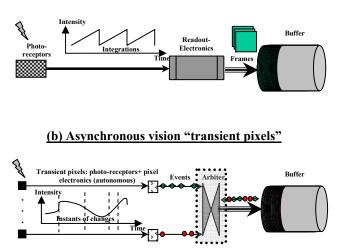

Clock-based vision systems permanently output frames with fixed size at a fixed time interval. Such an image frame is the result of the integration of light intensity using a number of photo-receptors for a predefined exposure time. These resulting light intensity integrations are sequentially read out and stocked in a buffer in a form of frames. Fig. 1(a) depicts an illustration of a clock-based vision system including photo-receptors, readout electronics and a data buffer. The temporal contrast vision sensors consist of a set of transient pixels, which autonomously and individually react to relative intensity changes. This sensor asynchronously outputs events, which represent the address of the spiking pixels and the type of the intensity change (ON: for intensity increase and OFF: for intensity decrease). These events have to be transferred through a shared bus to the buffer. In case of two pixels spiking at the same time instant a conflict will occur at the transfer level. Therefore an arbiter is needed.

The arbiter is the part of the AE communication interface [2] that aims to transmit all AE lossless in arbitrating between temporally coincident events. The arbiter deals with handling the organisation and the transfer of the AE through a shared communication bus to a buffer. Fig. 1(b) shows an illustration of the asynchronous optical sensor including the transient pixels, the arbiter and the buffer.

The output of the temporal contrast vision sensor [8] consists of a stream of arbitrated AE. These AE data provide the information on the individual pixel addresses that experience the light intensity changes but do not contain the occurrence time of the changes. For this reason, a synchronous AE interface with an internal time stamp assignment [7] has been designed.

#### (a)Clock-based vision systems

Fig. 1. Illustration of vision sensor principles: (a) clock-based systems, (b) asynchronous vision sensor with transient pixels.

### III. SYNCHRONOUS ADDRESS-EVENTS COMMUNICATION INTERFACE

In addition to arbitrating between coincident pixel events, the synchronous arbiter [7] performs the timestamp assignment with respect to the occurrence of an event at the arbiter input. They are generated using a continuous counting device and assigning the current counter value to the events. The timestamps are combined with the corresponding AE to compose a stream of data packets, which are called timed AE (TAE) at the output of the arbiter. Events with the same timestamp value are interpreted as concurrent and are arbitrated according to descending addresses.

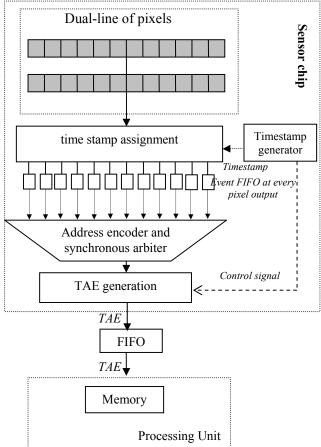

Fig. 2. Address-Event communication using the synchronous arbiter

Fig. 2 presents the process of generating TAE using the synchronous arbiter implemented in a dual-line vision sensor. A timestamp is attached on-chip to the AE data with a temporal resolution of 100ns at the input stage of the arbiter. Therefore, the output of the sensor consists of TAE with the AE and their accurate occurrence time. In order to avoid data loss, an event FIFO is placed at the output of every pixel in order to handle peak data rates and allow

storage of the pixels' data in cases where the synchronous arbiter is temporarily saturated.

The dual-line sensor includes the two communication interfaces (asynchronous and synchronous), which have been implemented in a 0.35  $\mu$ m standard CMOS process. The asynchronous AE interface covers about 7.5% while the synchronous AE interface covers 31% of the whole chip area. Indeed, by including the timestamp generator and the event FIFOs, the AE interface requires more space. However, by changing from the current 0.35 $\mu$ m design to a 0.18 $\mu$ m process, the synchronous AE interface size can shrink by 80%.

#### IV. PERFROMANCE ANAYLSIS AND EXPERIMENTAL RESULTS

The dual-line sensors chip [13] has implemented the arbitration concepts: asynchronous arbiter and synchronous arbiter as digital circuits, to handle temporally coincident pixels' events. Only one arbitration concept can be active at a time. The dual-line sensor consists of two lines of 256 autonomous pixels, which asynchronously respond to relative illumination changes. The sensor performance using the asynchronous and synchronous arbiter as summarized in TABLE I.

TABLE I.

DUAL-LINE SENSOR PERFROMANCE ANALYSIS USING THE ASYNCHRNOUS AND THE SYNCHRNOUS ARBITER

| Characteristics                   | Asynchronous Arbiter    | Synchronous Arbiter                                                                          |

|-----------------------------------|-------------------------|----------------------------------------------------------------------------------------------|

| Arbitration<br>behavior           | Not deterministic       | Deterministic (pixel<br>address in a<br>descending order per<br>timestamp)                   |

| Data<br>organization              | Random                  | Timestamp + pixel<br>addresses in<br>decreasing order                                        |

| On-chip<br>temporal<br>resolution | No time quantization    | ≥ 100ns                                                                                      |

| Peak input data<br>rate           | 10 <sup>6</sup> Event/s | 2.56 10 <sup>9</sup> Event/s @20<br>MHz system clock<br>frequency                            |

| Peak output<br>data rate          | 10 <sup>6</sup> Event/s | 10 <sup>7</sup> Event/s @20 MHz<br>system clock<br>frequency                                 |

| Handling of<br>Peak data rate     | None                    | Event FIFOs included<br>to minimize data loss<br>and to maintain the<br>temporal information |

| Possibility for<br>pixel masking  | No                      | Yes                                                                                          |

| Clock frequency                   | No clock                | 10-40 MHz                                                                                    |

From the analysis of the theoretical characteristics of the asynchronous and the synchronous arbiters, it can be noticed that the asynchronous arbiter arbitration behavior is not deterministic and the temporal information is not preserved within the AE interface. However, the synchronous arbiter

includes the time information to the AE and thus preserves the high temporal resolution aspect of the pixels. This advantage has a consequent influence on the dual-line sensor performance in capturing high-speed moving objects by preserving the object shape. The experimental evaluation of both arbiters is provided in the next section.

Both communication interfaces are implemented in the dual-line sensor chip and only one interface can be activated at a time for data acquisition. For evaluating the arbitration performance, we activated the synchronous arbiter and captured a high-speed moving object in a scene. Then we activated the asynchronous arbiter and captured the same object and we compared afterwards both object representations between both acquisitions.

#### A. Evaluation using a High-Bandwidth Light Source

In the first test, a laser light flashing instantaneously at all pixels has been used in order to evaluate the arbitration performance between the coincident events. All 512 pixels  $(2\times256)$  have to instantaneously send events as a reaction to the laser light flash. As all pixels events are temporally coincident, this test is adequate for evaluating the efficiency of both arbiter concepts to route all the events through the shared communication bus.

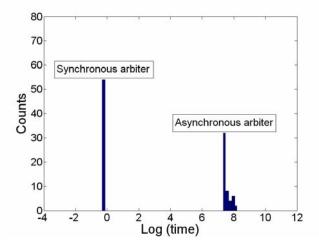

Fig. 3. Histogram of the arbitration duration with the synchronous (left) and asynchronous arbiter (right) for several measurements.

Fig. 3 depicts the statistical evaluation of the arbitration duration for several measurements with both arbitres. The x-axis (the arbitration duration) is represented in a logaritmic scale in order to plot both histograms (of the synchronous and asynchronous arbiters in one figure). The synchronous arbiter shows an arbitration duration within the selected time stamp resolution of 0.8  $\mu$ s which means that all events generated are assigned the same time stamp. The arbitration duration duration of the asynchronous arbiter lies between 1.6 ms and 3.5 ms for handling all 512 coincident events.

## B. Evaluation by Capturing High-Speed Moving Objects

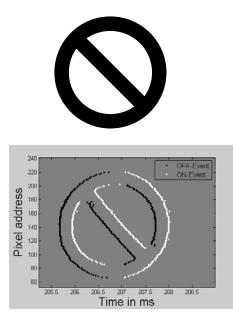

In this test, objects crossing the sensor field of view at ultra high-speed are used for evaluating the synchronous arbitration process. Several 2-D objects have been fixed on a rotating drum generating an object velocity greater than 15 m/s, and the corresponding TAE data have been acquired. The main evaluation criterion is the capturing and high-speed object representation performance of the dual-line sensor using the synchronous TAE interface. Fig.4 shows an original object (Top) and its TAE representation at a velocity of 25 m/s using the dual-line sensor with activated synchronous arbiter (Bottom). The synchronous arbiter supports the temporal contrast vision sensor in preserving its main advantage "the high-temporal resolution" in efficiently handling concurrent TAE and thus supporting high-speed applications.

Fig. 4. Original object (top) and its AE representation using the dual-line sensor with synchronous arbitration (bottom)

The synchronous arbitration efficiently handles coincident pixel events with high accuracy and minimal data loss that maintain the original shape structure. Moreover, due to the deterministic behavior of the synchronous arbitration, the data stream with sorted AE data is advantageous for vision applications in terms of algorithmic efficiency.

#### V. CONCLUSIONS

An evaluation of the synchronous address-event communication interface for temporally concurrent pixel events from biologically-inspired (neuromorphic) vision sensors is presented. By including a timestamp assignment mechanism and an event FIFO for every pixel on-chip, the synchronous address-event interface preserves the fundamental advantage for neuromorphic temporal contrast vision sensors that is the ultra-high temporal resolution of the pixel activities, to make the system attractive for high speed vision applications. Furthermore, the synchronous arbitration process is deterministic and offers possibility to handle higher peak rates than those for the asynchronous arbiter and thus yield to minimal data loss. Moreover, this synchronous address-event interface and its digital integration allow masking and unmasking pixels in the array to adapt the sensor to different applications.

#### REFERENCES

- A.N. Belbachir, M. Litzenberger, C. Posch and P. Schön, "Real-Time Vision Using a Smart Sensor System," in the International Symposium on Industrial Electronics, ISIE2007, Spain, June 2007.

- [2] K. A. Boahen, "Point-to-point connectivity between neuromorphic chips using address events," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 47, no. 5, pp. 416–434, May 2000.

- [3] K. A. Boahen, "A burst-mode word-serial address-event link—I: Transmitter design," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 7, pp. 1269–1280, Jul. 2004.

- [4] J. Costas-Santos, T. Serrano-Gotarredona, R. Serrano-Gotarredona and B. Linares-Barranco, "A Spatial Contrast Retina with On-chip Calibration for Neuromorphic Spike-Based AER Vision Systems," IEEE Trans. CAS, vol. 54, No. 7, pp. 1444-1458, July 2007.

- [5] E. Culurciello, R. Etienne-Cummings, K. Boahen, "Arbitrated Address Event Representation Digital Image Sensor," ISSCC Dig. Tech. Papers, pp. 92–93, Feb. 2001

- [6] T. Delbrück, "Silicon Retina with Correlation-Based, Velocity-Tuned Pixels," IEEE Transactions on Neural Networks, Vol. 4, No. 3, pp. 529-541, 1993.

- [7] M. Hofstätter, A.N. Belbachir, E. Bodenstorfer and P. Schön, "Multiple Input Digital Arbiter with Timestamp Assignment for Asynchronous Sensor Arrays," IEEE ICECS06, Nice, France, 2006.

- [8] P. Lichtsteiner, C. Posch and T. Delbrück, "A 128×128 120dB 15us Latency Asynchronous Temporal Contrast Vision Sensor," IEEE Journal of Solid State Circuits, Vol. 43, pp. 566 - 576, Feb. 2008.

- [9] S.-C. Liu, J. Kramer, G. Indiveri, T. Delbrück, T. Burg, and R. Douglas, "Orientation-selective aVLSI spiking neurons," Neural Networks, Special Issue on Spiking Neurons in Neuroscience and Technology, 14(6/7), pgs 629-643, 2001.

- [10] M. A. Mahowald and C. A. Mead, "A Silicon Model of Early Visual Processing," Neural Networks, vol. 1, pp. 91-97, 1988.

- [11] M. A. Mahowald and C. A. Mead, "Silicon Retina," in C. A. Mead, Analog VLSI and Neural Systems. Reading, pp. 257-278, MA: Addison-Wesley, 1989.

- [12] C. Mead, "Neuromorphic Electronic Systems," Proceedings of the IEEE Volume 78, Issue 10 pp. 1629-1636, Oct 1990

- [13] C. Posch, M. Hofstätter, D. Matolin, G. Vanstraelen, P. Schön, N. Donath and M. Litzenberger, "A Dual-Line Optical Transient Sensor with On-chip Precision Timestamp Generation," IEEE International Conference on Solid-State Circuits, USA, February 2007.